第四部分 数据中心光学:挑战

基于 FPP 模块的数据中心光学设备持续发展的主要障碍是缺少超800G的发展路线、高成本、电通道功耗大以及由于带宽密度有限而对机架空间需求不断增加。本节更详细地讨论这些方面。

4.1 超800G

目前还没有支持超800G的可插拔模块。就所需的电连接器和光连接器密度而言,在相同尺寸内将通道数量增加或超过8个极具有挑战性。

超800G 的可插拔模块可能需要更大的外形尺寸来应对散热问题,这种尺寸的增加会对带宽密度产生负面影响。

更高的通道速率不可避免,≥200 Gb/s 的直接检测光学技术已经证明可行,但用于FPP光模块的200 Gb/s 电 Serdes 的实际可行性尚不确定。

尽管这种 Serdes 可能在 PCB、连接器和封装得到显著改进的情况下有一定可行,但芯片到模块的通道可能需要 LR 型(30 dB 插损)。交换机 ASIC 和模块功耗的相应增加,是未来可能考虑CPO技术的强大动力。

4.2 成本

在过去 10 年中,光模块的单位容量平均成本大幅下降,见图 2a。工艺技术、集成度和制造技术的改进是主要原因。然而,在很大程度上,这种极端的价格下降也归因于一小群强大的用户“超大规模数据中心运营商”,他们对成本有高度的敏感性。

图2 2010-2023年以太网交换机和光模块成本趋势;2020-2023 年的值是预测值。

然而,交换机 ASIC 单位容量成本下降的速度比光学器件的成本下降得更快。这导致光学器件在交换机的总成本中所占的相对成本增加。如图2b所示,这个比率在从 10G 到 400G 的增加很快。对于 400G 一代,预计光学器件将占总成本的 50% 以上。

主要原因是交换机ASIC在这一时期充分受益于摩尔定律,而光模块则没有。传统(非硅光子)光学模块是复杂的微光学系统,由许多分立元件制成,通常是手工组装,并以相对较高的封装成本进行低密度封装。为了迎头赶上,需要提高集成和制造自动化水平。为了保持光学器件的相对成本恒定,光学器件的单位容量成本需要与交换机 ASIC 的成本和总容量(的倒数)保持同步。硅光是实现这一目标的关键技术。

图3将 400G 收发器模块的成本分解为收发器子组件、接收器子组件、机械组件(PCB、微控制器、无源器件、连接器、外壳等)以及最终组装和测试。大约 40% 的成本与组装和测试有关。CPO 可以通过消除大部分与封装相关的分立部件和组装步骤来大幅降低这一份额,同时通过晶圆级集成、封装和测试降低发射和接收子组件的制造成本。

图 3 400Gb/s可插拔收发器的成本结构细分

4.3 密度

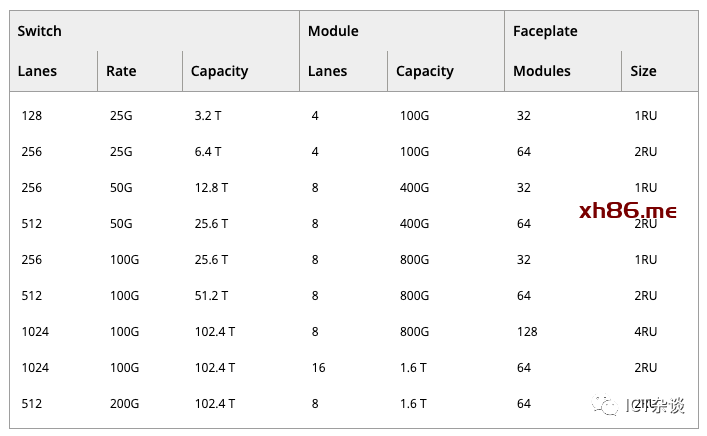

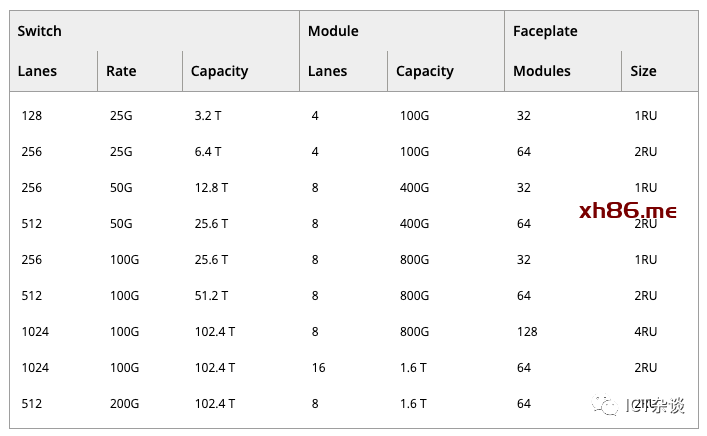

带宽密度是另一个重要的限制因素。表4总结了带宽密度的发展。对于 1.28 和 3.2 T 交换机,1RU标准设备可分别容纳 32 个 40G 和 100G 的 QSFP 模块。6.4T(64×100G)则需要采用2RU,因为密度更高的光模块当时并没有准备好。对于 12.8 T 代,交换ASIC和光学器件再次对齐:8通道 QSPF-DD/OSFP 400G 模块的可用性使得在 1RU 盒体中容纳12.8T成为可能。

表 4 带宽密度

采用50G Serdes速率的25.6T芯片要容纳64×400G QSFP-DD光模块需要2RU空间。而当速率转换到100G Serdes时,又采用1RU(32×800G)就可以实现。然而,散热也成为一个问题。400G FR4和DR4模块的功耗在10-12W左右,所以单个盒体在640-768W。加上主交换机ASIC、控制CPU、风扇和电源,整机最终在 1.5-2 kW之间。由于对散热器尺寸、面板通风率和风机性能的情况,这需要一个很强的散热解决方案,而该解决方案可能难以在1RU中解决。

当交换机达到51.2T时,2RU空间可以容纳64×800G模块,如果散热可行,采用可插拔模块似乎可以达到51.2T这一代。

但是,超800G到底该如何?是必须要解决的问题。板载和共封装解决方案的优点是面板侧仅需要无源光连接器即可。他们尺寸很小,在面板侧可以容纳更多的通道,也可以留出更多的通风面积。而且这些无源器件没有热量,不需要考虑自身的散热。

板载光学联盟 (COBO) 定义了一种 16 通道板载模块,支持800 Gb/s,100G Serdes,每个模块还可以达到1.6T,但目前似乎没有朝这个方向继续努力。尽管 COBO 模块释放了面板空间,但它们占用了主 PCB 上的大量空间(COBO 模块宽 20 毫米,长 60 毫米),且需要自己的散热器,而且还不能堆叠。

总而言之,在 51.2 T这一代之后,外形尺寸的变化是不可避免的,无论是新的可插拔、板载或共同封装技术下,都不可避免。这给新的一些方案提供了机会。

4.4 功耗

可插拔模块的主要挑战是功耗。问题的核心在于在 ASIC 和模块之间的电通道中信号完整性遭受到了挑战。这使得模块和交换机 ASIC 的功耗不断升高。图4显示了随着交换机发展,Serdes功耗在ASIC芯片上功耗占比的增加情况,对于25.6T这一代芯片,Serdes功耗占比超过30%。

图 4 Serdes功耗占比

可插拔模块的额定功耗从 SFP 模块的 2 W 增加到 QSFP 模块的 3.5 W,现在 QSFP-DD(功率等级 8)超过 14 W,OSFP(功率等级 8)超过 21.1 W。当前 400G 收发器的额定功耗约为 10-12 W 。

7nm DSP 芯片可以支持基于 100G (<20 pJ/bit)电 Serdes 的下一代 400G 和 800G 模块。但对于单个800G模块,也是轻松超过OSFP 和 QSFP-DD 额定功耗限制。这意味着 51.2T交换机仅光模块功耗就大约1kW。

光模块功耗的最大贡献者是模块和ASIC之间的电传输通道。在当前的 400G 光模块中,这通常是一个分立的芯片,在八个电通道和四个光通道之间执行时钟和数据恢复 (CDR)、数字信号处理 (DSP) 和Gearbox等功能。图5是代表性400G光模块的功耗分解图,分别光学引擎(激光器、调制器/驱动器、检测器/TIA)、电气 I/O(CDR/DSP/Gearbox)、微控制器(uCtrl)和电源转换(DC/DC)等。

图 5 400 Gb/s 可插拔光模块功耗细分

随着信号速率的增加,通道上的电损耗一直在增加。从 NRZ 到 PAM4 的转变以较低的信噪比为代价提供了数据速率的增长,因此需要使用FEC将信号加倍至 56 Gbd 以获得 112 Gb/s速率,对于给定长度的低损耗 PCB 走线,插损(以 dB 为单位)大约会加倍;即使使用先进的 PCB 材料,12″ trace在28G Nyquist频率下的插损也为 15–20 dB ,这显然超出了VSR预期。电通道越短,转换越少,信号完整性问题就越容易管理,这促使将光学器件移到内部,尽可能靠近ASIC。

另外,散热正在成为密度方面的一个限制因素,包括交换机散热器的尺寸、面板所需的最小开孔率、盒体机箱内的气流和风机等。

原则上,CPO 不仅可以简化模块,还可以简化ASIC,例如通过用 XSR Serdes 替换 LR serdes。然而,这是以牺牲灵活性为代价的。即使采用 CPO,LR 也有两个明确的方案,即一方面用于服务器连接的铜质 DAC,另一方面用于数据中心间链路的相干光学 (ZR)。由于相干光学在短期内不太可能适合共封装技术,因此此类端口仍然需要支持可插拔。

另一种方法是利用强大的ASIC能力来大幅简化光引擎(消除 CDR)。CPO 供应商需要与交换机供应商密切合作,共同设计最高密度和最低功耗的整体解决方案。

未完待续……

5 移动光器件到内部

5.1 板载光学技术

5.2 共封装光学技术

5.3 方案与路径

5.3.1 铜

5.3.2 光学PMD

5.3.3 可达性

5.3.4 生态系统

5.3.5 成熟度

5.4 标准化

5.5 CPO 要求

5.6 光子集成

6 网络架构演进

7 结论